云岫资本指出,SiC产业链具有显著的价值量倒挂情况,衬底的壁垒最高,价值量最大。根据云岫资本,SiC衬底的核心壁垒在于晶体生长,缺陷控制难度很高。据悉,SiC存在200多种晶型,仅4H晶型可以用于制造SiC衬底,晶体生长过程需要精确控制生长温度梯度、气流气压以及晶体生长速率等参数,否则容易产生多晶型夹杂;此外,SiC晶体生长过程中缺乏有效的监控手段,非常依赖公司在长晶工艺方面的积累。云岫资本还指出,SiC外延缺陷会影响器件良率,所以衬底质量至关重要。例如:SiC外延致命性缺陷将导致器件击穿电压大幅降低(20~90%),大大降低良率。使用地应力、低位错密度的衬底原材料能够避免衬底缺陷向外延延伸,提高外延产品的良率。未来随着衬底成本的下降,外延价格有望持续降低。

封装技术向小型化、高密度引脚、高效散热方向演变

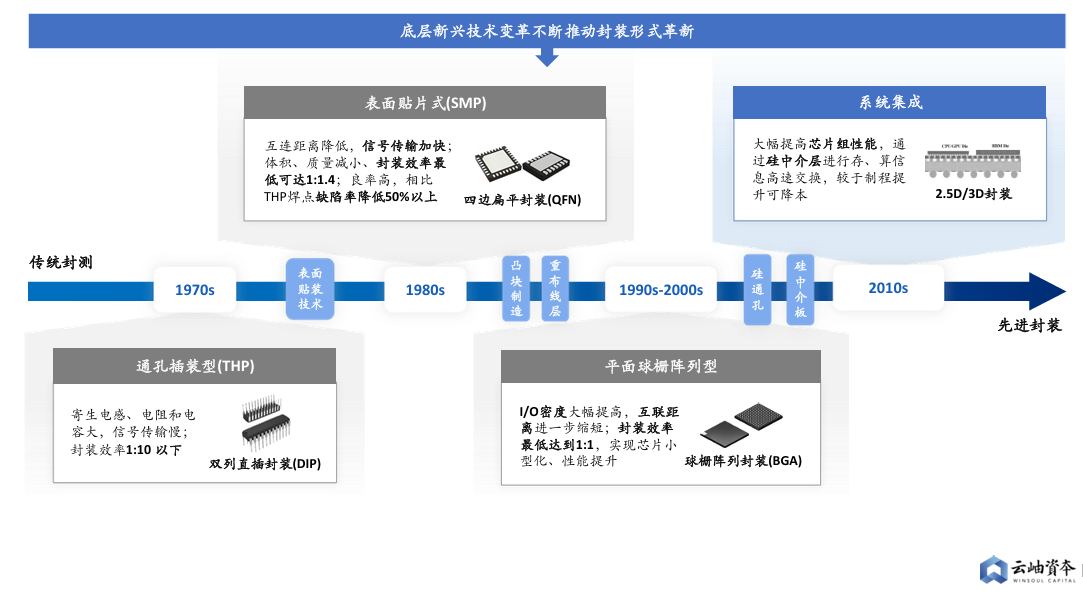

从历史看,半导体封装经历了三次重大发展,底层技术的发展推动了封装结构形式的革新。封装技术的发展历史可以归纳为从有线连接到无线连接,从芯片级封装到晶圆级封装,从二维封装到三维封装的演变。先进封装技术如3D IC、异构集成等,为芯片设计提供了更多可能性,也为封装行业带来了新的增长点。

图:底层新兴技术变革不断推动封装形式革新

Bump、RDL、TSV和Wafer技术提高芯片集成度

根据云岫资本,先进封装I/O数量多、芯片小、高度集成化,四大底层技术为Bump、RDL、TSV和Wafer。

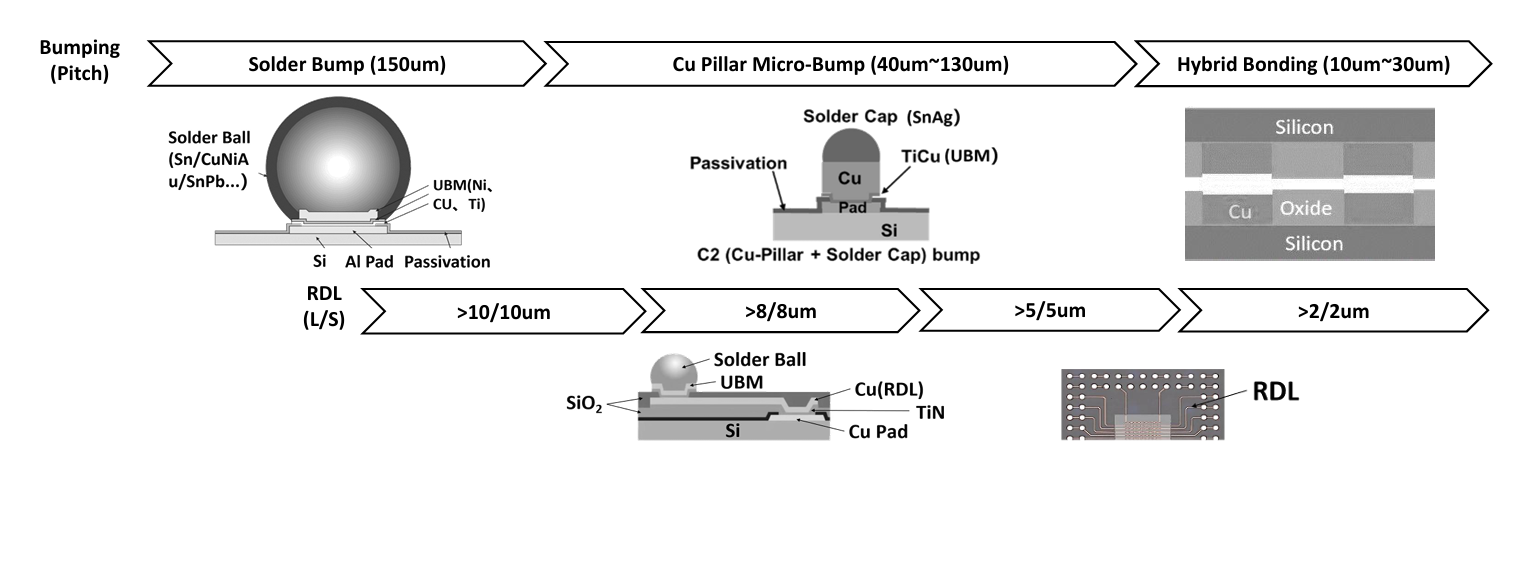

Bumping(凸块制造技术):Bump技术通过在芯片表面制作微小的金属凸点,为芯片提供了电气互连的“点”接口。这种技术显著缩短了电气连接路径,降低了信号损耗,提升了分布电感,从而更适合高速信号传输。Bump技术的实现推动了多种先进封装方式的发展,如倒装芯片(Flip Chip)、晶圆级封装(WLP)和扇出型封装(Fan-out Package)等。这些封装方式不仅提高了芯片的集成度,还实现了更高的封装效率和更低的成本。

Bump技术使得封装密度大幅提升,因为凸块可以在芯片表面形成更多的I/O接口,从而增强了数据处理带宽。此外,随着凸块制备工艺的不断创新,凸块的尺寸和间距也在不断缩小,进一步提高了芯片的集成度和性能。

图:横向维度更高效的互连

RDL技术(重布线层):RDL工艺在先进封装领域发挥着越来越重要的作用。它通过在晶圆表面沉积金属层和介质层并形成相应的金属布线图形,对芯片的I/O端口进行重新布局。这种重新布局不仅缓解了I/O端口拥挤的问题,还为先进封装技术如3D封装、扇出型封装(FOWLP)等提供了强有力的支持。

RDL技术使得芯片能够拥有更多的I/O数量,从而满足日益增长的数据传输需求。此外,RDL还优化了芯片的I/O布局,提高了数据传输效率,为芯片的小型化、集成化提供了有力支持。

TSV技术(硅通孔):TSV是一种关键的垂直互连技术,它通过在芯片内部打通的通道实现了电气信号的垂直传输。TSV技术可以显著提高芯片之间的数据传输效率,减少信号延迟,降低功耗,并提升封装的集成密度。

在2.5D封装中,TSV主要应用于需要高度互连和高带宽的系统,如高性能计算和数据中心芯片。而在3D封装中,TSV实现了芯片的垂直堆叠,每个芯片层通过TSV直接相互连接,形成一个整体。这种垂直集成的方式允许不同功能模块(如处理器和内存)高度集成在同一个封装中,显著提高了芯片的集成密度和性能。

Wafer技术(晶圆):Wafer技术可以用作芯片的基底和WLP封装的载体,也可以与硅基板一同实现2.5D集成。随着晶圆面积的不断增大和工艺技术的不断进步,晶圆技术为提高芯片集成度提供了更多的可能性。

在晶圆级封装(WLP)中,晶圆技术使得封装后的芯片尺寸与裸芯片几乎一致,符合消费类电子产品轻、小、短、薄化的市场趋势。此外,晶圆技术还支持多种先进封装方式的发展,如扇入式晶圆级封装(FIWLP)和扇出式晶圆级封装(FOWLP)等,这些封装方式进一步提高了芯片的集成度和性能。

相关阅读: