2025年5月29日,在荷兰阿姆斯特丹举办的欧洲技术研讨会上,台积电再次明确表示,在其1.6nm(A16)与1.4nm(A14)工艺节点中,将不会采用下一代高数值孔径极紫外光刻光刻技术。这一表态延续了台积电一贯的审慎策略,凸显其通过挖掘现有低数值孔径极紫外光刻技术潜力、不断优化制程工艺来突破技术瓶颈的技术路径。

高数值孔径极紫外光刻的技术价值与台积电的考量

高数值孔径极紫外光刻由ASML主导开发,是当前最受关注的新一代光刻技术,其分辨率提升至约8nm,相较传统低数值孔径极紫外光刻技术(13.5nm)大幅提高,理论上可支持3nm以下制程的单次曝光,从而降低多重曝光所带来的复杂度。然而,High-NA设备不仅价格高昂(单台超过3亿美元),且在工艺整合、光罩控制、平整度等方面要求极高,目前仅英特尔等少数公司计划在2027至2028年导入用于14A工艺。

台积电副联席COO张凯文在会上表示:“我们只有在高数值孔径极紫外光刻真正带来明确、可量化的优势时才会导入。目前A14节点通过优化现有技术,已经能够实现目标性能。”

他指出,台积电将继续依赖低数值孔径极紫外光刻技术,通过多重曝光、图形自对准(与设计规则创新等方式,持续推进制程微缩,而无需立即引入High-NA。

A14:不靠新光刻,也能实现“全节点”升级

A14是台积电计划于2028年量产的下一代先进制程节点,其技术优势不仅体现在制程尺度的微缩,更在于器件结构与标准单元架构的深度创新:

第二代全环绕栅极晶体管(GAA):通过纳米片结构优化,进一步提升电流驱动能力与栅极控制精度,相较前代制程在相同性能下可降低25~30%功耗,或在相同功耗下提升15%的性能。

新一代标准单元设计:针对不同电路类型(逻辑、存储、模拟)进行结构重构,在不牺牲良率的前提下,提高整体晶体管密度。逻辑电路密度提升达23%。

深度挖掘低数值孔径极紫外光刻技术潜力:结合多次曝光与计算光刻等技术,突破传统分辨率极限。虽然张凯文未透露具体技术实现,但他表示团队已找到在不依赖High-NA的前提下,完成A14节点制程的方法。

值得关注的是,A14后续版本(预计2029年引入背面供电网络SPR)同样不会使用高数值孔径极紫外光刻,进一步佐证台积电对现有光刻体系的信心。

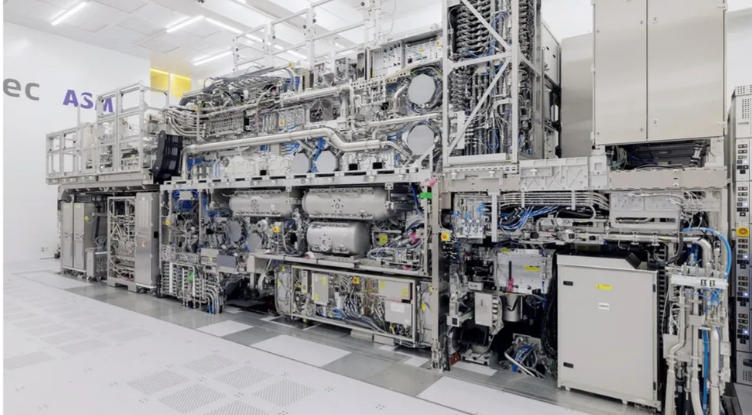

图:台积电:1.4nm工艺无需高数值孔径极紫外光刻(图源:ASML)

不同路线:台积电与英特尔的技术战略分歧

英特尔与台积电在先进制程策略上的差异,愈发明显。英特尔倾向通过高数值孔径极紫外光刻来简化制程,减少多重曝光带来的套刻误差,并计划于14A节点引入该技术。而台积电则更重视既有设备的成熟度和整体制造生态的稳定性,选择以设计与工艺协同创新来化解光刻压力。

这种差异源自两家公司不同的商业模式:英特尔作为IDM厂商,更愿意通过新设备导入简化内部流程;而台积电作为纯代工企业,则需在满足客户需求、控制成本与降低技术风险之间取得最优平衡。毕竟,高数值孔径极紫外光刻不仅意味着巨额设备投入,还伴随厂房升级、供应链重组等系统性成本。

High-NA的“最佳时机”仍未到来

尽管当前并不急于导入高数值孔径极紫外光刻,台积电并未否定其长远价值。张凯文指出,High-NA终将成为先进制程的一环,但“必须等到技术、成本与客户需求三者契合的关键时刻”。

未来是否采用高数值孔径极紫外光刻,将取决于多方面因素:

制程物理极限的逼近:若在3nm以下节点,多重曝光的复杂度与成本持续攀升,而High-NA的单次曝光能带来更优解,则技术切换将水到渠成。

设备成熟度提升与成本下降:随着ASML计划于2025年交付首批High-NA设备,未来几年其制造与维护成本有望逐步降低。

客户需求牵引:若主要客户(如苹果、高通)对先进封装或异构集成提出更高图形精度要求,也可能推动技术导入时间提前。

光刻路线分岔:渐进 vs 颠覆

台积电的最新表态,折射出其在摩尔定律放缓背景下的“渐进主义”路线:通过深度优化现有技术体系,实现性能与良率的持续提升,而非急于拥抱尚不成熟的颠覆性技术。尽管这一策略可能面临多重曝光带来的良率挑战,但它避免了高昂投入与不确定风险。

从行业格局来看,英特尔与台积电正走在两条截然不同的路径上:一边是希望通过高数值孔径极紫外光刻迅速冲破制程限制的“颠覆派”,一边是依靠现有体系逐步优化的“稳健派”。而未来谁能在性能、成本与规模化量产之间取得最佳平衡,仍有待市场验证。