在台积电(TSMC)周三举办的北美技术研讨会上,该公司展示了其半导体技术与芯片封装技术的未来发展蓝图。半导体技术的发展对于维持摩尔定律的传统部分至关重要,而芯片封装技术的创新则可能推动处理器向着由更多硅材料构成的方向快速发展,最终实现与完整硅晶圆尺寸相当的系统。台积电透露,特斯拉下一代的Dojo训练芯片已经在生产中,而到了2027年,台积电计划推出比特斯拉所使用的更为复杂的晶圆级系统技术,预计这些技术将提供比现有系统高达40倍的计算能力。

过去数十年,芯片制造商主要通过缩小晶体管占用的面积和互连尺寸来提高处理器上的逻辑密度。然而,这种单纯依靠缩小尺寸的方法已经逐步接近其物理极限。因此,行业正在转向使用更先进的封装技术,这使得单个处理器能够集成更多的硅材料。单个芯片的最大尺寸受限于光刻设备能够制造的最大图案尺寸,即所谓的光罩尺寸限制,目前大约为800平方毫米。如果您希望在图形处理单元(GPU)中集成更多的硅材料,则需要通过多个芯片来实现。关键在于如何将这些芯片连接起来,以便信号能够在它们之间高效、低能耗地传输,就如同它们是一整块硅材料一样。

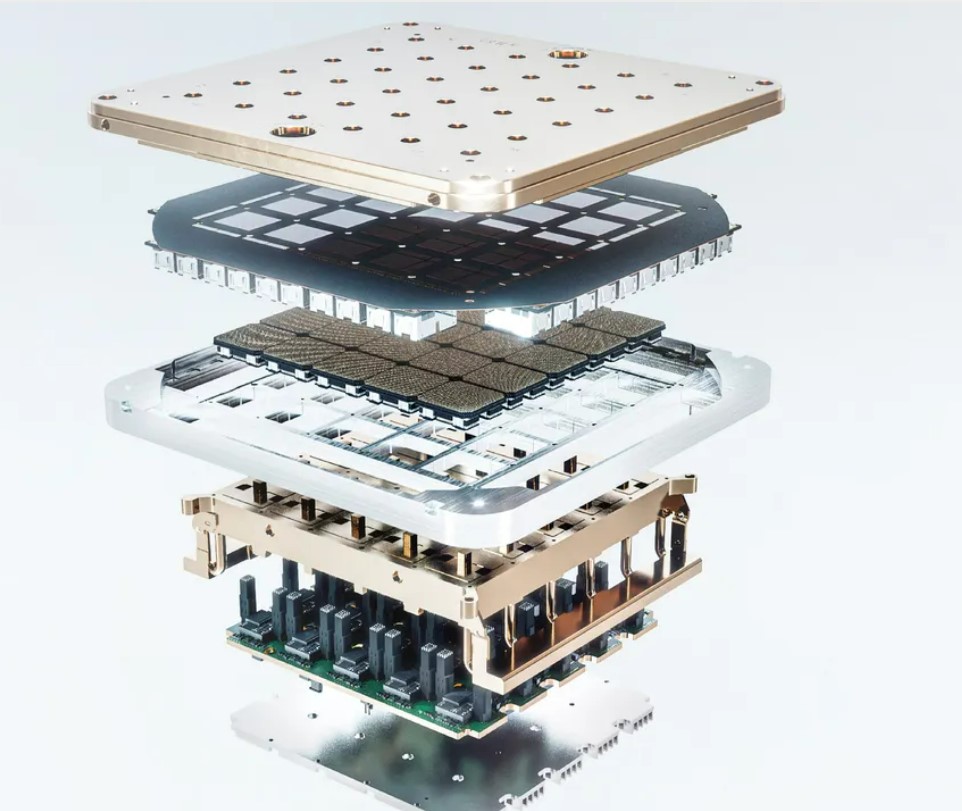

图一:台积电预计2027年推出更高级的晶圆级系统

台积电已经为Cerebras公司制造了一种晶圆尺寸的人工智能加速器,但这种合作模式似乎是独一无二的,并且与台积电目前提出的“晶圆级系统”(System-on-Wafer)有所不同。

然而,台积电在其首轮推出的“晶圆级系统”(System-on-Wafer)中,为解决光罩限制和良品率问题提供了一种不同的解决方案。该方案从已经测试合格的逻辑芯片开始,以尽量减少缺陷。这些芯片被放置在载板上,芯片间的空白区域被有效利用。然后,利用台积电的集成扇出技术构建一层高密度互连层,以实现芯片间的连接,目标是实现芯片间的数据传输带宽极大化,让它们在功能上如同一个单一的大型芯片。

到2027年,台积电计划利用其更先进的封装技术——晶圆上芯片封装(CoWoS)——提供晶圆级的集成解决方案。在这项技术中,预先测试合格的逻辑芯片以及重要的高带宽内存,将被安装在一个已经布满高密度互连线路的硅衬底上,并通过被称为硅通孔的垂直连接贯穿。附加的逻辑芯片也可以利用台积电的3D芯片技术,即系统级集成芯片(SoIC)。

CoWoS的晶圆级版本代表了封装技术的扩展,这种技术在高端GPU中已经显现。例如,Nvidia的下一代GPU——Blackwell,就采用了CoWos技术,集成了超过3个光罩尺寸大小的硅片,包括8个高带宽内存(HBM)芯片。到2026年,Nvidia计划将这一规模扩大到5.5个光罩尺寸,包括12个HBM。台积电表示,这将使其计算能力超过2023年技术的3.5倍以上。但到了2027年,台积电预计能够实现的是一个完整的晶圆集成,其计算能力将是现有技术的40倍,相当于超过40个光罩尺寸的硅片,并且有足够的空间容纳超过60个HBM。