随着芯片速度需求的不断增长,需要通过将更多能量传输到日益微缩的器件上来实现,从而导致了电流密度的增加,这对长期的芯片可靠性构成了威胁。尽管这个问题已被广泛认知,但在前沿设计中对其进行控制却变得越来越困难。

特别值得关注的是电迁移问题,在具有多个芯片片的先进封装中,电迁移问题愈发棘手。其中,各种键合和互连方案会带来材料和几何形状的突变。例如,电子可能会从铜线路流动到锡银铜(SAC)焊料凸点,然后转向基于镍的凹点金属层,最后流入中继器的铜垫。这种流动可能导致原子的移动,进而引发高密度扇出封装中的焊点失效或铜重分布层的故障。

在微电子封装中,特别是随着集成电路的微型化和集成度的提高,微焊点间的距离越来越小,导致互连焊点中的电流密度不断增加。这种高电流密度环境下,电迁移现象会导致金属互连线上形成空洞、小丘或凸起,破坏焊点,进而影响整个电路的可靠性。具体来说,电迁移可能导致以下问题:

空洞:金属互连结构上的空洞出现将导致电路的断路或线路电阻的增加,从而引起电路功能的失效。

小丘(或晶须):小丘(或晶须)的出现将导致相邻互连的短路,导致极其严重的可靠性问题。

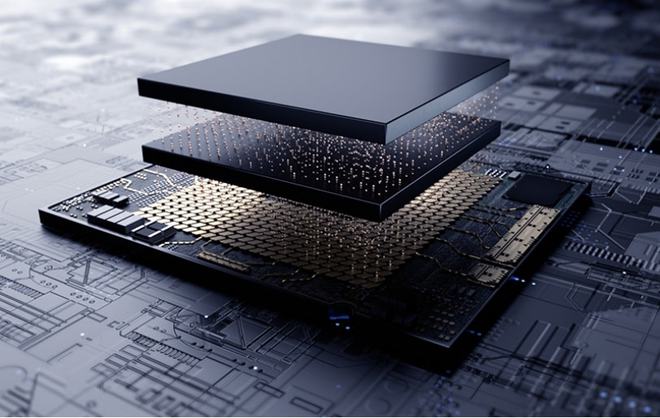

图:先进封装中电迁移问题日益严重

特别是在超大规模集成电路(VLSI)的发展中,芯片的功率越来越大而尺寸越来越小,使得互连结构的电流密度急剧增大,电迁移失效就更易出现。因此,国际半导体技术发展蓝图(ITRS)已将电迁移列为电子封装可靠性问题之一,并认为它是限制高密度封装发展的一个关键因素。

为了解决电迁移带来的问题,研究者们正在不断探索新的封装技术和材料。例如,一些新型的封装技术,如系统级封装、芯片级封装和异构集成封装等,能够通过将不同工艺、材料和结构的芯片集成在一起,提高芯片性能和功能密度,同时减少电迁移的发生。此外,新型的材料,如低电阻率和高熔点的材料,也被用于减少电迁移的影响。

总的来说,电迁移是先进封装技术中需要重点关注和解决的问题之一。通过不断的技术创新和材料研发,可以有效地减少电迁移的影响,提高微电子封装的可靠性和性能。例如优化电路设计,合理进行电路版图设计及热设计,尽可能增加条宽,降低电流密度,这有助于减少电迁移的发生。