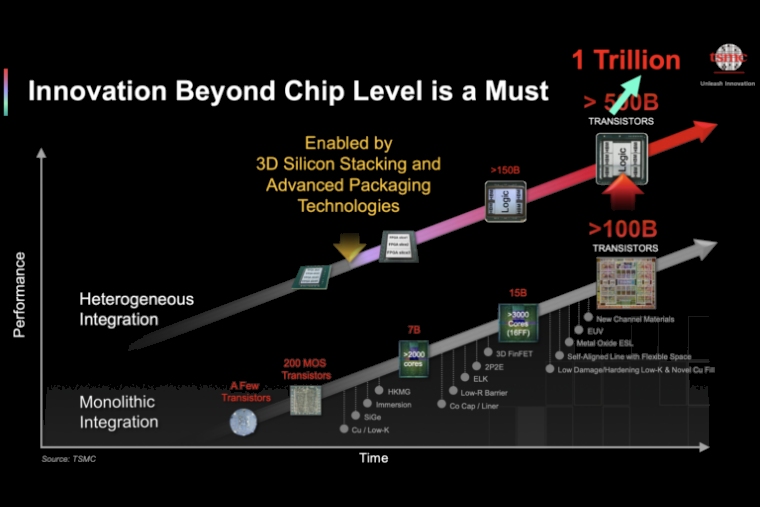

新思科技宣布将继续与台积电紧密合作,致力于在台积电的先进工艺和 3DFabric 技术上提供领先的 EDA 和 IP 解决方案,以推动 AI 和多芯片设计的创新。随着 AI 应用计算需求的不断上升,半导体技术必须加速发展。新思科技与台积电的合作,涵盖了由 Synopsys.AI 驱动的先进 EDA 套件,以及助力向 2.5/3D 多芯片架构转型的全面解决方案,旨在为未来数十亿至数万亿晶体管的 AI 芯片设计铺平道路。

台积电生态系统与联盟管理部负责人Dan Kochpatcharin表示:“我们很高兴与新思科技合作,开发先进的 EDA 和 IP 解决方案,以满足台积电 3DFabric 技术和先进工艺下对 AI 设计的高计算需求。我们在新思科技的 AI 驱动 EDA 套件及经过硅验证的 IP 方面的最新成果,显著提高了客户的生产力,并为 AI 芯片设计提供了卓越的性能、功耗和面积效果。”

新思科技 EDA 产品管理高级副总裁 Sanjay Bali强调:“数十年来,新思科技与台积电紧密合作,提供涵盖所有先进节点的关键 EDA 和 IP 解决方案。此次合作对加速 AI 时代的创新、推动半导体设计的未来发展具有重要意义。我们在性能、能效和工程效率方面取得了显著突破。”

通过 Synopsys.AI提供支持的 AI 驱动 EDA 流程,行业领导者已开始在 N2 工艺上应用这一解决方案,以提升 PPA 和工程生产力。联发科技副总裁吴清山表示:“新思科技经过认证的定制编译器和 PrimeSim 解决方案提高了我们的设计性能和生产率,帮助我们满足台积电 N2 工艺高性能模拟设计的要求。与新思科技的合作让我们能够充分利用其 AI 驱动流程的潜力,加速设计迁移和优化。”

图:新思科技与台积电合作实现万亿晶体管

此外,新思科技还与台积电合作,为其数字设计流程开发了新的背面布线功能,以优化电源分配和信号布线,从而提升设计效率和密度。可互操作工艺设计套件(iPDK)和 Synopsys IC Validator 物理验证工具可帮助设计团队高效应对复杂的物理验证规则,并顺利过渡到台积电的 N2 技术。

为了进一步加速芯片设计,新思科技与台积电通过云认证将其 EDA 工具部署到云端,为客户提供云端解决方案。这些工具能够提供准确的结果质量,并与台积电的先进工艺技术无缝集成,包括综合、布局布线、静态时序和功耗分析等功能。

在推动多芯片设计的创新方面,新思科技、Ansys和台积电合作,通过全面的系统分析流程解决多芯片设计所面临的复杂挑战。最新的流程基于 Synopsys 3DIC Compiler 平台,集成了3DSO.AI,与 Ansys RedHawk-SC™数字和 3D 集成电路电源完整性验证平台相结合,增强了热和 IR 感知的时序分析能力。Synopsys 3DIC Compiler 是经过台积电认证的平台,支持 3Dblox 和台积电的 3DFabric 技术,包括 TSMC-SoIC® 和 CoWoS 封装技术。

Ansys 半导体、电子和光学业务副总裁兼总经理John Lee表示:“我们与 Synopsys 和台积电的合作体现了我们共同推动创新和实现 AI 及多芯片设计未来的承诺。我们合作应对多芯片架构的多物理挑战,帮助客户在基于台积电最新技术的 Synopsys 设计环境中实现芯片、封装和系统级效果的精准验证。”

为降低风险,Synopsys 提供的全面多芯片测试解决方案与Synopsys UCIe和 HBM3 IP一起,确保多芯片封装在制造和现场测试中的健康状况。通过与台积电的合作,Synopsys 已采用台积电的 CoWoS 中介层技术成功流片一款测试芯片,全面支持测试、监控、调试和修复功能,以实现设计、生产和现场的优化。

Synopsys 在 N3E 和 N5 工艺技术上成功实现了多项 UCIe 和 HBM3 IP 解决方案的流片,推动 IP 集成并降低风险。Synopsys UCIe IP 的最新进展可实现高达 40G 的运行速度,在不增加额外面积的情况下实现最大带宽和能效,而 HBM4 和 3DIO IP 解决方案则加速了在台积电先进工艺下的 3D 堆叠芯片的异构集成。