半导体互连技术作为芯片制造的关键环节,正处于重大变革的前夜。发布于semiengineering 的Interconnects Approach Tipping Point,主要围绕半导体制造中互连技术的变革展开讨论,深入剖析了随着芯片制程逼近10埃节点,互连技术面临的挑战以及即将到来的材料与工艺革新。文章的作者是一位有着丰富半导体经验的编辑,无论是行业从业者,还是对半导体技术发展感兴趣的读者,都能从这篇文章中获取到关于钌、钼等新型互连材料,以及相关创新工艺的前沿信息,深入了解半导体互连领域的未来走向。下面中国出海半导体出海小编将对文章的核心内容进行解读:

在半导体制造领域,互连技术正处于重大变革的边缘。随着芯片制造工艺朝着10埃节点迈进,新的架构、工具和材料呼之欲出,这将极大改变晶圆厂构建互连的方式。其中,大马士革工艺在当前的半导体互连制造中占据着重要地位,且与未来的变革密切相关。

大马士革工艺分为单大马士革工艺和双大马士革工艺,是一种广泛应用于半导体制造中金属互连层形成的技术。以双大马士革工艺为例,在进行金属互连层制造时,会先在介质层(通常是电介质绝缘体)上蚀刻出沟槽和通孔,然后通过特定的工艺将金属(如铜)填充进去 。在填充过程中,一般先填充通孔,再填充沟槽,以此形成金属互连线路,实现芯片中不同器件之间的电气连接。

目前在铜互连中,大马士革工艺应用广泛。但随着芯片制程不断缩小,向更先进的节点发展,该工艺也暴露出一些问题。例如,在微小的线宽和节距下,铜互连需要添加阻挡层、衬垫层和帽层等,以防止铜扩散到相邻区域,并为电镀填充提供良好的条件。然而,这些额外的层不仅占据了宝贵的导体空间,而且其自身的电阻率比铜高,导致整体电阻增加。像在10nm宽的线路中,沉积TaN阻挡层、钴衬垫层和钴帽层后,实际有效的铜宽度可能只有4nm - 5nm。此外,随着互连节距接近20nm,传统的大马士革工艺在通过电镀填充微小间隙时,沉积工具越来越难以保证填充无缺陷或无空洞。比如,互连节距变小时,减薄钴衬垫会导致铜润湿性变差,进而引发可靠性问题。

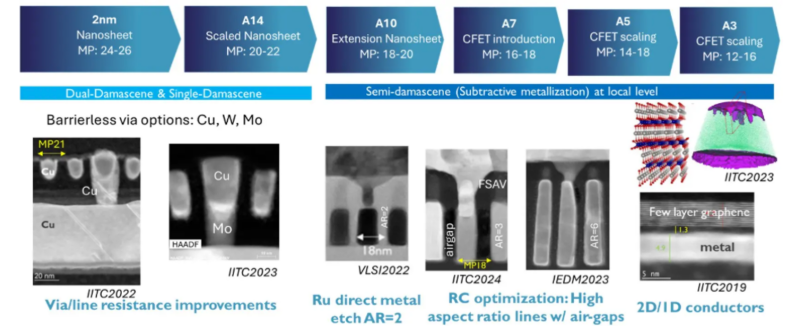

图:钌和气隙半镶嵌工艺路线图。(来源:imec)

随着行业向更先进的制程发展,如10埃节点,为了应对这些挑战,可能需要对工艺进行调整。一种趋势是从基于大马士革工艺的流程转向减成法沉积 - 蚀刻流程。以钌互连为例,虽然现有大马士革工艺可用于钌互连,但减成法更具优势,它能减少紧密尺寸下线条的摆动和扭曲,实现更高纵横比的线条制造,与未来的CFET结构更兼容。不过,转向新的工艺并非易事,需要解决一系列的技术难题,确保新工艺满足大规模生产的可靠性等要求。

目前,随着先进逻辑器件向新一代纳米片结构发展,其互连面临严峻挑战。1纳米(10埃)节点下,虽然金属线节距达20纳米且线宽更大,但互连堆栈已消耗器件三分之一的功率,并占据芯片75%的RC延迟。为解决这些问题,行业急需更优质的导体。尽管目前铜基解决方案在晶圆厂仍被广泛使用,但从铜到替代金属的转变已在筹备之中。

在众多替代方案中,钌(Ru)和钼(Mo)备受关注。钌可能最早在14埃节点时,用于替换最底层、最紧密连接层的铜互连。许多领先的逻辑晶圆厂,如台积电、英特尔、IBM研究中心和三星等,都在研究基于钌的互连集成方案。钌无需阻挡层,可直接蚀刻,不易氧化,电子平均自由程短,能降低短线路宽度下散射对电阻的影响。此外,采用减成法蚀刻取代现有大马士革工艺,可减少线条在紧密尺寸下的摆动和扭曲,实现更高纵横比的线条制造,更适配未来的CFET结构。不过,将气隙集成到器件中虽能降低电容,但会降低机械稳定性,因此气隙可能会交替且少量使用。

钼则有望成为用于DRAM和3D NAND的钨互连的继任者。几乎所有大型芯片制造商都在对钼在NAND、DRAM和逻辑应用中的使用进行不同阶段的评估。钼除了与现有大马士革工艺兼容、无需阻挡层外,成本较低也是其一大优势。通过离子束沉积在400°C下沉积钼,可获得比钨更低的电阻率,且能优化晶粒结构。

在彻底转换材料之前,芯片制造商仍在对现有基于铜和钨的互连流程进行改进。例如,在双大马士革工艺中,通过采用低电阻过孔工艺、原子层沉积更薄的TaN扩散阻挡层、使用替代衬垫(如钌 - 钴)以及消除过孔底部的阻挡层等方式,来提升性能。三星就曾报道过优化钌 - 钴衬垫,以改善3纳米节点下的铜间隙填充效果。

除了材料变革,互连制造方式也在发生重大变化。背面功率传输(BPD)技术将功率传输转移到晶圆背面,使晶体管上方的互连层仅用于传输信号。这一变革能放宽晶圆正面的金属节距要求,可能推迟钌在某些器件节点的引入。

但这些变革并非一蹴而就。从基于大马士革工艺的流程转向减成法沉积 - 蚀刻流程,以及从铜到钌的材料转变,对逻辑制造商的互连工艺而言是巨大的颠覆性变化。实现钼互连的工艺也在快速发展,旨在寻找最佳的材料和设备组合。在半导体行业,只有当现有流程无法满足性能要求时,才会推动材料和架构的变革。鉴于在铜双大马士革和钨金属化的工具、材料和工艺配方上投入巨大,任何金属替代都将循序渐进地进行。