在最近举办的一场存储器大会上,半导体行业领头羊三星公司公布了其充满雄心壮志的技术发展蓝图。该蓝图涵盖了3D DRAM和堆叠DRAM等技术,三星预测这些技术有望在本十年内逐步推出。不过,根据三星最新发布的技术路线图所示,首个3D DRAM技术节点预计至少还需要经历两代产品的迭代,因此,目前手上的DDR4内存条还不必急于更换。在最近召开的MemCon会议上,三星公司向公众展示了其最新的技术成果。其中最引人注目的是3D DRAM技术,据三星公司表示,三星计划在2025年将其推向市场。此外,该公司还透露了堆叠式DRAM技术的发展计划,预计将在2030年前后投入商用。根据记者Fred Chen在X网站发布的相关信息,3D DRAM将采用名为垂直通道晶体管(VCT)的先进技术VCT技术,通过将晶体管的沟道方向从水平变为垂直,大幅减少了器件面积的占用,同时提高了对刻蚀工艺精度的要求。而堆叠DRAM技术则充分利用了Z轴向的空间,在较小的面积内容纳更多的存储单元,单芯片的存储容量有望提升至100G以上。这种VCT实质上是一种FinFET晶体管,也有可能是全包围栅(GAA)设计。但根据观察,三星在VCT的初期版本中更倾向于使用前者的设计。这意味着三星在技术创新的道路上又迈出了坚实的一步,为未来的半导体市场带来了更多可能性。三星公司表示,一旦其半导体制程技术突破10纳米大关,公司将着手生产业界首款3D DRAM产品。目前,三星正在采用12纳米工艺生产DRAM,并计划在过渡到更先进的制程之前,推出两个基于10纳米的工艺节点。按照计划,这一转变将在2025年左右实现。据预测,3D DRAM的推出将大幅提升存储性能和容量,尽管三星尚未透漏具体的性能提升数据

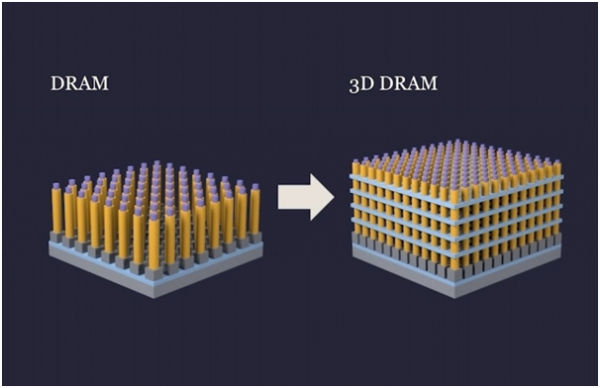

图一:3D DRAM

就目前来看,三星似乎打算推出包含垂直堆叠电路的3D DRAM模块,这与AMD的V-Cache设计类似,这一模块的推出可能会显著提升容量。一旦完成部署,该公司可能会着手将多个这样的模块层叠起来,形成一个3D内存立方体塔,类似于目前高宽带内存(HBM)的制造方式。目前这种内存每个立方体最多有八层,但预计2025年将发展至12层。

根据市场研究机构的预测,3D DRAM市场有望在2028年达到1000亿美元的规模。这一技术的商业化将数据中心、高性能计算、人工智能等领域带来巨大的性能提升。为了保持在竞争中的领先地位,三星已在美国硅谷设立了新的3D DRAM研发实验室,专注于开发下一代高性能内存解决方案。三星在3D DRAM技术上的突破不仅是对现有存储技术的重大改进,也是对未来计算需求的前瞻性响应。随着制程技术的响应,我们有理由相信,3D DRAM技术将开启一个高性能、高效率的内存新时代,为全球的信息技术发展提供强有力的支持。