在半导体行业的快速发展中,Cadence Design Systems, Inc.(以下简称Cadence)以其最新的Palladium Z3 Emulation和Protium X3 FPGA Prototyping系统,再次证明了其在高性能硬件验证与调试领域的领先地位。这两款系统不仅在性能上实现了1.5倍的加速,而且在容量上也实现了超过2倍的增长,为复杂的SoC芯片和系统提供了更高的性能、容量和调试能力。

一、提升性能,加速创新

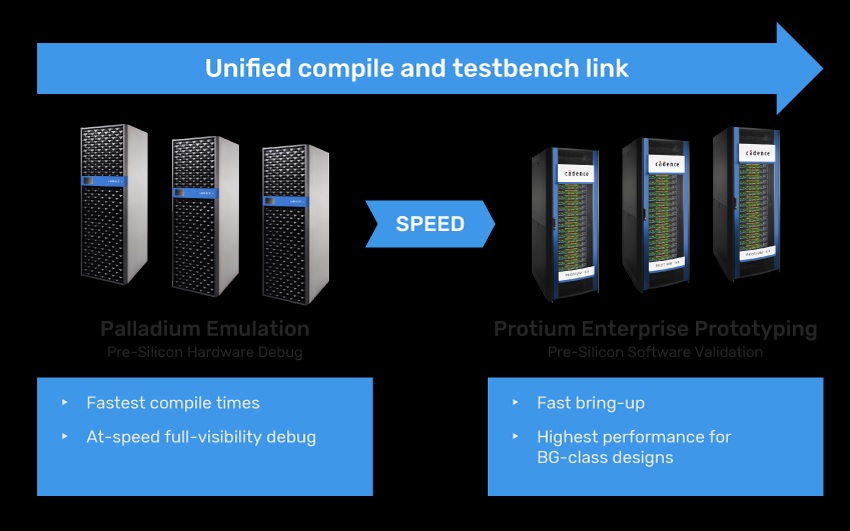

Cadence的Palladium Z3系统,以其新的定制Cadence仿真处理器,提供了业界最快的编译速度和全面的硅前硬件调试功能。性能的提升意味着客户可以在更短的时间内完成更多的设计验证迭代,每天可以完成多次设计验证迭代,这在以往的技术中是难以想象的。Protium X3系统则以其快速的初始环境搭建能力,为十亿门级设计的硅前软件验证提供了强有力的支持。

二、数字孪生技术的新高度

数字孪生技术通过创建虚拟模型映射物理实体,实现实时监测、预测维护与优化决策。Cadence的Palladium Z3和Protium X3系统正是基于这一理念,通过提供无缝集成的流程、统一的编译器和通用的虚拟及物理接口,实现了设计从硬件仿真平台到原型验证平台的快速迁移。这种集成不仅提高了验证的效率,也为客户提供了更高的验证吞吐量,确保硬件创新产品能够更快地推向市场。

三、应对复杂设计,推动AI和高性能计算

随着SoC设计的复杂性日益增加,Palladium Z3和Protium X3系统提供了从1600万门到480亿门的测试规模,使得超大型SoC可以进行整体测试,确保了适当的功能和性能。这种规模的测试能力,对于AI、汽车和数据中心应用中的Arm IP设计创新至关重要。Cadence的系统正在推动这些领域的设计创新,为共同客户带来显著的益处。

四、合作与集成,提升性能与可扩展性

Cadence与NVIDIA的合作,使得Palladium Z3和Protium X3系统采用了NVIDIA BlueField DPU和NVIDIA Quantum InfiniBand网络连接器,这不仅保证了系统间切换的一致性,也实现了虚拟接口与物理接口之间的自由转换。此外,AMD也与Cadence合作,将AMD Versal™ Premium VP1902自适应SoC集成到Protium X3系统中,并将基于AMD EPYC™处理器的主机服务器集成到Palladium Z3和Protium X3系统中,以提高容量,实现更高的性能和可扩展性。

图:Cadence Palladium Z3 Emulation和Protium X3 FPGA Prototyping系统,紧密集成的动态系统组合

五、结论

Cadence的Palladium Z3和Protium X3系统不仅是性能上的怪兽,更是数字孪生技术革命的引领者。它们通过提升性能、加速创新、应对复杂设计,以及推动AI和高性能计算的发展,为半导体行业带来了新的活力。随着这些系统的部署和应用,我们有理由相信,Cadence将继续在智能系统设计领域保持其领导者的地位。